CMOS(Complementary MOS)는 NMOS와 PMOS로 이루어진 상보대칭형 구조이다.

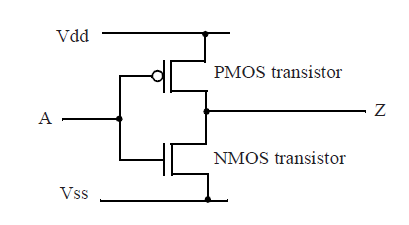

아래는 대표적인 CMOS 인버터로 input A가 1일때 PMOS는 turn off NMOS는 turn on되어 output z가 0되고 input A가 0일때 PMOS는 turn on NMOS는 turn off되어 output z가 1되는 구조이다. 더 정확한 표현은 Vdd로 pull up Vss pull down된다고 해야할 것이다.

이러한 CMOS inverter는 가장 기존 형태의 CMOS logic이고 이러한 상보대칭형 구조로 NAND,NOR 등등 가능한데 NAND의 구조를 한번 보자

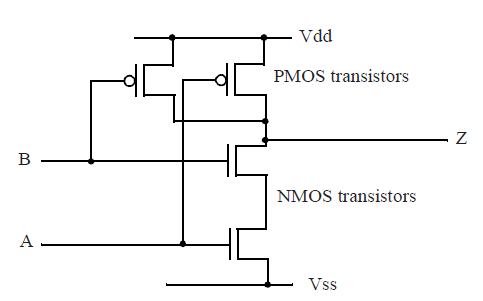

2 input NAND 역시 pull-up구조와 pull-down구조가 상보 대칭형으로 구성되어있다. A와 B가 모두 low일때 Z가 1이고 그 이외의 경우는 Z가 0이다.

A and B 일때 PMOS 모두 turn off 되어 pull-up구조가 off되고, NMOS가 둘다 turn on되고 pull-down구조가 turn off 된다.

~A or ~B 일때 PMOS 중 하나 이상이 turn on 되어 pull-up구조가 on되고, NMOS 하나 이상이 turn off되고 pull-down구조가 turn off 된다.

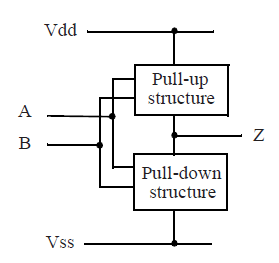

즉 pull-up구조와 pull-down구조는 하나가 turn on되면 반드시 다른 하나는 turn off되는 항상 반대로 작동하기 때문에 상보대칭형 구조이라는 것이다.

이러한 특성의 장점은 단일 tr또는 pass tr구조보다 controlability가 크다.

**실제로 CMOS에서 transition 구간에서 둘다 pull-up와 pull-down구조 모두 on하여 power leakge가 일시적으로 생기는데 power부분에서 따로 자세한 설명을 하겠다.

다음은 CMOS로 이루어진 Cell에 대해서 정리를 하겠다.

'VLSI > VLSI기초' 카테고리의 다른 글

| SPEF(Standard Parasitic Exchange Format) 기초 (0) | 2022.02.24 |

|---|---|

| lsf(Load Sharing Facility) (0) | 2020.08.11 |

| [VLSI기초 - CMOS logic] 3. Modeling of CMOS Cells (0) | 2020.05.25 |

| [VLSI기초 - CMOS logic] 2. Cell - Standard Cell (0) | 2020.05.25 |

| [VLSI기초 - CMOS logic] 0. MOSFET(NMOS, PMOS) (0) | 2020.05.25 |

댓글